The research activities are organized towards the analysis and design of analog and digital electronic circuits implementing nonlinear dynamical systems, with a special reference to the following research lines:

- Implementation of Physically Unclonable Functions (PUFs) to be used as cryptographic primitives for challenge/response chip authentication;

- Generation of random binary sequences for cryptographic applications;

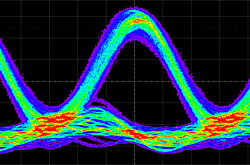

- Generation of analog stochastic signals for the statistical testing of ADCs, electronic circuits and instrumentation.

Detailed Research Activities

The research activities focus on the following topics:

- Efficient implementation of 1D chaotic maps with full-custom or semi-custom (FPGAs) digital circuits, for the definition of cryptographic pseudo-random number generator;

- Theoretical analysis and design techniques to enhance the entropy of random number generator circuits;

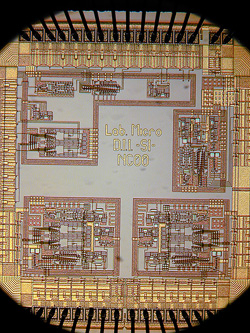

- Design of analog electronic circuits implementing cryptographic true-random number generators based on chaotic dynamical systems (with analysis of the nonidealities introduced by the chip fabrication process tolerances and mismatches);

- Theoretical analysis of the dynamics in nonlinear perturbed systems;

- Generation of analog stochastic signals for the statistical testing of ADCs, electronic circuits and instrumentation;

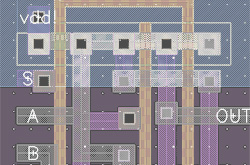

- Statistical analysis and design of digital circuits implementing Physically Unclonable Functions (PUFs) based on ring-oscillators;

- Analysis and design of analog electronic circuits implementing Physically Unclonable Functions (PUFs) based on nonlinear systems derived from Cellular Neural Networks (CNNs).

IEEE keywords

Nonlinear Circuits; Cryptography; Random Number Generation; Nonlinear Dynamical Systems; Chaos; Cellular Neural Networks; Mixed Analog Digital Integrated Circuits; Authentication; Testing; Stochastic Systems; Field Programmable Gate Arrays.

ERC keywords

PE7_2 Electrical and electronic engineering: semiconductors, components, systems

PE7_5 Micro- and nanoelectronics, optoelectronics

PE7_7 Signal processing

PE6_5 Cryptology, security, privacy, quantum crypto

Selected Publications

- T. Addabbo, M. Di Marco, A. Fort, M. Mugnaini, H. Takaloo and V. Vignoli, "A CMOS PUF Circuit Primitive Based on a Two-Dimensional Nonlinear Dynamical System," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019, pp. 1-5.

- T. Addabbo, A. Fort, M. Mugnaini, H. Takaloo, V. Vignoli and N. Petra, "Piecewise Linear Chaotic Maps in Current Mode CMOS Circuits: Nonlinear Distortion Analysis," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019, pp. 1-5.

- T. Addabbo, A. Fort, R. Moretti, M. Mugnaini, V. Vignoli and M. Garcia Bosque, "Lightweight True Random Bit Generators in PLDs: Figures of Merit and Performance Comparison," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 2019, pp. 1-5.

- T. Addabbo, A. Fort, M. Mugnaini, V. Vignoli and M. Garcia-Bosque, "Digital Nonlinear Oscillators in PLDs: Pitfalls and Open Perspectives for a Novel Class of True Random Number Generators," 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, 2018, pp. 1-5.

- Acosta, A. J., Addabbo, T., and Tena‐Sánchez, E. ( 2017) Embedded electronic circuits for cryptography, hardware security and true random number generation: an overview. Int. J. Circ. Theor. Appl., 45: 145– 169.

- Addabbo, T., Fort, A., Di Marco, M., Pancioni, L., Vignoli, V.,"A demonstration circuit implementing 1-bit Physically Unclonable Functions based on two-neurons CNNs", (2014) International Workshop on Cellular Nanoscale Networks and their Applications.

- Addabbo, T., Fort, A., Di Marco, M., Pancioni, L., Vignoli, V., "Physically unclonable functions derived from cellular neural networks", (2013) IEEE Transactions on Circuits and Systems I: Regular Papers, 60 (12), pp. 3205-3214

- Addabbo, T., De Caro, D., Fort, A., Petra, N., Rocchi, S., Vignoli, V., "Efficient implementation of pseudochaotic piecewise linear maps with high digitization accuracies", (2012) International Journal of Circuit Theory and Applications, 40 (1), pp. 1-14.

- Addabbo, T., Fort, A., Rocchi, S., Vignoli, V., "Digitized chaos for pseudo-random number generation in cryptography", (2011) Studies in Computational Intelligence, 354, pp. 67-97.

- Addabbo, T., Fort, A., Kocarev, L., Rocchi, S., Vignoli, V., "Pseudo-chaotic lossy compression of TRBGs", (2011) Proceedings - IEEE International Symposium on Circuits and Systems, art. no. 5937979, pp. 1980-1983.

- Addabbo, T., Fort, A., Kocarev, L., Rocchi, S., Vignoli, V., "Pseudo-chaotic lossy compressors for true random number generation", (2011) IEEE Transactions on Circuits and Systems I: Regular Papers, 58 (8), art. no. 5710440, pp. 1897-1909.

- Addabbo, T., Alioto, M., Fort, A., Rocchi, S., Vignoli, V., "A variability-tolerant feedback technique for throughput maximization of TRBGs with predefined entropy", (2010) Journal of Circuits, Systems and Computers, 19 (4), pp. 879-895.

- Addabbo, T., Fort, A., Rocchi, S., Vignoli, V., "Exploiting chaotic dynamics for A-D converter testing", (2010) International Journal of Bifurcation and Chaos, 20 (4), pp. 1099-1118

- Addabbo, T., Fort, A., Papini, D., Rocchi, S., Vignoli, V., "An efficient and accurate method for the estimation of entropy and other dynamical invariants for piecewise affine chaotic maps", (2009) International Journal of Bifurcation and Chaos, 19 (12), pp. 4175-4195

- Addabbo, T., Kocarev, L., "Periodic dynamics in queuing networks", (2009) Chaos, Solitons and Fractals, 41 (4), pp. 2178-2192.

- Addabbo, T., Fort, A., Papini, D., Rocchi, S., Vignoli, V., "Invariant measures of tunable chaotic sources: Robustness analysis and efficient estimation", (2009) IEEE Transactions on Circuits and Systems I: Regular Papers, 56 (4), pp. 806-819.

- Addabbo, T., Fort, A., Rocchi, S., Vignoli, V., "Chaos based generation of true random bits", (2009) Studies in Computational Intelligence, 184, pp. 355-377.

- Addabbo, T., Alioto, M., Fort, A., Pasini, A., Rocchi, S., Vignoli, V., "A class of maximum-period nonlinear congruential generators derived from the rényi chaotic map", (2007) IEEE Transactions on Circuits and Systems I: Regular Papers, 54 (4), pp. 816-828.

- Addabbo, T., Alioto, M., Fort, A., Rocchi, S., Vignoli, V., "A feedback strategy to improve the entropy of a chaos-based random bit generator", (2006) IEEE Transactions on Circuits and Systems I: Regular Papers, 53 (2), pp. 326-337.

- Addabbo, T., Alioto, M., Fort, A., Rocchi, S., Vignoli, V., "The digital tent map: Performance analysis and optimized design as a low-complexity source of pseudorandom bits", (2006) IEEE Transactions on Instrumentation and Measurement, 55 (5), pp. 1451-1458.

- Addabbo, T., Alioto, M., Fort, A., Rocchi, S., Vignoli, V., "Low-hardware complexity PRBGs based on a piecewise-linear chaotic map", (2006) IEEE Transactions on Circuits and Systems II: Express Briefs, 53 (5), pp. 329-333.